11.1 - ¿Qué es un registro de desplazamiento?

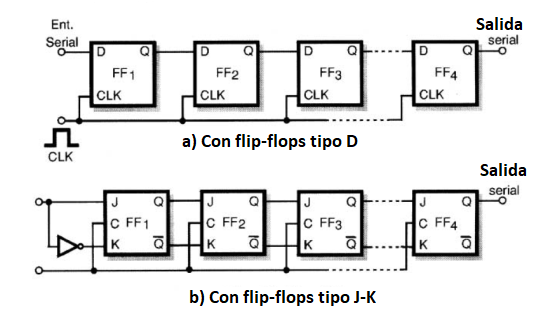

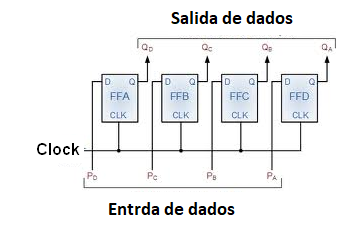

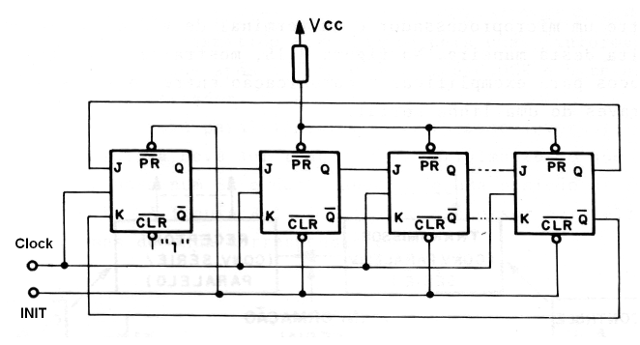

Un registrador de desplazamiento o "shift-register", como también es llamado por el término inglés, es un conjunto de flip-flops que pueden ser interconectados de una variedad de maneras, por ejemplo, como se muestra en la figura 82.

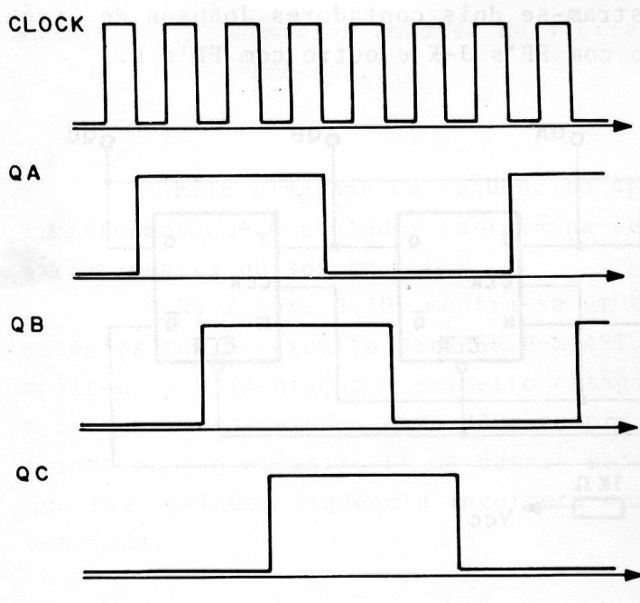

Estos circuitos pueden desplazar la información (bit) aplicada en la entrada de una posición, a cada pulso del clock. Por ejemplo, el bit 1 aplicado a la entrada aparece en la salida del primer flip-flop en el primer pulso de clock, luego los cambios que aparecen en la salida del segundo flip-flop, en el segundo pulso de clock, y así sucesivamente, hasta que aparece al final de la secuencia, como se muestra en la figura 83.

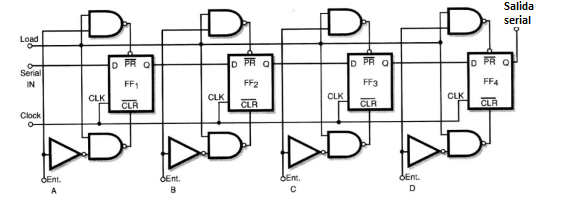

En la configuración que se muestra en la figura 1 (a), cada tipo de flip-flop D tiene su salida conectada a la siguiente entrada flip-flop, y todas ellas están controladas por la misma señal de CLOCK.

Para entender cómo funciona este circuito comenzaremos desde la situación inicial donde todos están desactivados o con sus salidas Q a bajo nivel.

Inicialmente, se aplicará a la entrada de datos un nivel alto (1). Como podemos ver, es a entrada es hecha por la entrada de J del primer flip-flop (FF1).

Con la llegada del pulso del clock a este flip-flop, cambia de estado y con este "almacena" el pulso aplicada a la entrada, que aparece en su salida, después de un breve periodo de tiempo. Vea que esta señal es almacenada con el flanco positivo de la señal del clock, cuando entonces el nivel alto debe estar presente en la entrada del flip-flop.

El intervalo de tiempo que transcurre entre la aplicación de la señal en la entrada de datos y su aparición en la salida del flip-flop es el orden de algunos segundos en la integración de familias lógicas comunes, pero es importante que en muchas aplicaciones más rápidas se tome en cuenta.

Para aplicaciones muy rápidas, se da preferencia al uso de los circuitos integrados de algunas subfamilias TTL.

En el siguiente pulso del clock, algo interesante ocurre: la entrada del primer flip-flop no tiene más de alto nivel y por lo tanto FF1 no cambia estado. Sin embargo, en la salida de FF1 tenemos un nivel alto, y esta salida está conectada a la entrada del segundo flip-flop (FF2).

Esto significa que con la llegada del segundo pulso de clock, el nivel lógico de la primera salida se transfiere a la segunda salida, entonces, por supuesto, de un intervalo de tiempo pequeño, como se muestra en la tabla abajo.

A continuación, tenemos que, el bit 1 aplicado en la entrada, si "cambia" un poco más en el circuito, pasando a la salida del segundo flip-flop.

Por supuesto, si en este segundo pasaje, hemos aplicado un nuevo nivel 1 en la entrada del circuito, al mismo tiempo que los primeros traslados al segundo flip-flop, el segundo se desplaza a la salida del primer flip-flop, como se muestra en la figura 84.

Ahora que llega un tercer pulso clock, tendremos nueva transferencia y el nivel alto o el bit 1 se transfiere a la salida del siguiente flip-flop, es sea, FF3.

En otras palabras, en cada pulso de clock, los niveles existentes en las salidas flip-flop, ya sean 0 o 1, se transfieren al siguiente flip-flop.

Por lo tanto, suponiendo que apliquemos, en secuencia, en la entrada de un registro como los niveles indicados 0101, tendremos la siguiente secuencia de condiciones de salida para los flip-flop de un shft-register que usan 4 de ellos:

| Clock | Entrada | FF1 | FF2 | FF3 | FF4 |

| Início | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 |

| 2 | 1 | 0 | 1 | 0 | 0 |

| 3 | 0 | 1 | 0 | 1 | 0 |

| 4 | 0 | 0 | 1 | 0 | 1 |

Vea entonces que en el quinto pulso de clock, el primer pulso de clock, el primer nivel lógico, aparece a la salida del último flip-flop (FR4) y que, si leemos la salida de los flip-flops, habrá registrado los niveles aplicados en la entrada: 0101.

El lector debe haberse percibido ya que aplicando datos binarios en un shift-register, después del número apropiado de pulsos del clock, que corresponde al número de bits que el contiene, puede almacenar estos datos.

Para eliminar los datos en secuencia, simplemente siga aplicando pulsos de clock al circuito, como se muestra en la siguiente tabla:

| Clock | FF1 | FF2 | FF3 | FF4 | Salída |

| Início(4) | 0 | 1 | 0 | 1 | 1 |

| 5 | 0 | 0 | 1 | 0 | 0 |

| 6 | 0 | 0 | 0 | 1 | 1 |

| 7 | 0 | 0 | 0 | 0 | 0 |

La figura 85 muestra lo que ocurre en los detalles:

Tenga en cuenta que para almacenar un dato de 4 bits en un registrador, debemos aplicar 4 pulsos de clock y para leer en secuencia, más 4 pulsos de clock.

Para "borrar" los datos registrados en un shift-register, todos a la vez, como se indica, sólo tiene que aplicar un pulso en la entrada CLEAR.

Todos los flip-flops tendrán sus salidas tomadas en el nivel bajo o 0.

11.2 – Tipos de registros de desplazamiento

Dependiendo de cómo la información entra y cómo se puede obtener de un registro de desplazamiento, podemos tener varias configuraciones que nos llevan a varios tipos de circuitos.

Así que hay circuitos en los que tenemos una serie o dos de entrada, y también podemos tener una o dos líneas de salida.

A continuación, veremos los tipos principales como sus denominaciones.

SISO - Serial-in/serial out

En el ejemplo que tomamos, los datos se aplicaron a la entrada del registrador en forma de niveles lógicos uno tras otro, acompañando la señal del clock. Decimos que este registrador opera con la carga de datos "serial" o serie. En otras palabras, este circuito tiene entrada serie o serial-in.

Exactamente como ocurre con el puerta serie de un ordenador, los datos son " alienados ", entrando uno tras otro, quedando entonces almacenados en flip-flop, como se muestra en el circuito de la figura 86.

PISO - Para Parallel-in/Serial out

Sin embargo, existe una segunda posibilidad de operación para los shift-registers, que es la de operar con la entrada de datos en paralelo y salir con estos mismos datos en serie. Decimos que se trata de un shift-registers con entrada paralela y salida en serie.

En la figura 87 tenemos un diagrama que utiliza 4 flip-flops tipo D y que tiene entrada de datos paralela y salida en serie.

Analicemos cómo funciona:

Los datos se colocan al mismo tiempo en la entrada, ya que funciona en paralelo. Por ejemplo, si vamos a almacenar los datos 0110, estos detalles se aplican al mismo tiempo en las entradas correspondientes de los flip-flops.

En el primer pulso de clock, los flip-flops "almacenan" estos datos. Así, los flip-flops que tienen nivel 1 en su entrada S pasan este nivel a la salida (FF2, FF3). Por otro lado, los que tienen el nivel 0 en su entrada, mantienen este nivel en la salida (FF1 y FR4).

Esto significa que después del pulso del clock, las salidas de los flip-flop presentarán los niveles 0110.

SIPO-serial-in/paralelo-out

Del mismo modo, como se muestra en la Figura 88, podemos cargar los datos en serie y hacer su lectura en paralelo.

Los registros que operan de esta manera también se pueden denominar convertidores serie-paralelo o paralelos, según el modo de funcionamiento.

Este tipo de registrador es muy importante en la transmisión de datos a través de medios físicos (transmisión serial), ya que puede hacer su conversión a la forma digital normal de datos que llegan en serie, transmitidos por un módem.

PIPO - Parallel-in/Parallel-out

Estos son circuitos en los que los datos se cargan al mismo tiempo (paralelos), y luego se leen al mismo tiempo por las salidas de los flip-flops, como se muestra en la figura 89.

Los registros de desplazamiento se siguen clasificando según la dirección en la que se pueden desplazar los datos.

Decimos que este es el tipo Shift-Right cuando los datos se desplazan a la derecha y que es un tipo Shift- Left cuando los datos se desplazan a la izquierda sólo. (right = derecha, left = izquierda)

También hay tipos bidireccionales, como se muestra en la figura 90, donde los datos pueden ser desplazados en ambas direcciones. Este es un registrador del tipo SISO.

Vea que la dirección del desplazamiento está determinada por una entrada que actúa en las puertas que modifican el punto de aplicación de las señales en cada flip-flop, exactamente como estudiamos en los contadores de up y down de las lecciones anteriores.

Con la aplicación de un nivel lógico conveniente en la entrada LEFT/RIGHT, podemos determinar la dirección de desplazamiento de los datos en el circuito.

11.3 – Operando con binarios

Como ya ha notado el lector, los grabadores de desplazamiento pueden memorizar números binarios, recibirlos en serie o en paralelo y entregarlos posteriormente en serie o en paralelo.

En computadoras, calculadoras, módems, sistemas de transmisión de datos y muchos otros equipos digitales esta configuración es bastante Utilizado, tanto en la conversión de datos de los puertas, como en sus propias memorias, y otros circuitos internos.

Es interesante notar que en la configuración que tomamos como ejemplo, donde se utilizan 4 flip-flops, los bits almacenados siguen un cierto orden.

Así, cuando representamos el número 5 (0101), cada uno de los bits tiene un valor relativo, que depende de su posición en el número, o cantidad representada, como ya hemos estudiado en lecciones anteriores.

| bit | 0 | 1 | 0 | 1 | |

| valor | 8 | 4 | 2 | 1 | |

| no dado | 8x0 | 4x1 | 2x0 | 1x1 | |

| Total | 0 | 4 | 0 | 1 | =5 |

| MSB | LSB | ||||

MSB representa un bit más significativo, (Most Significant Bit), o sea, de mayor peso, mientras que LSB representa un bit menos significativo o de menor peso (Least Significant Bit, del inglés).

(Estamos trabajando con datos de 4 bits, no 8 como es común en las computadoras, obteniendo así el "byte", para mayor facilidad de comprensión-el grupo de 4 bits también se llama “nibble")

Luego se enlazan 4 flip-flops para obtener un shift-register, como se muestra en la figura 91, entrando con los datos de manera que el bit menos significativo sea el primero (LSB) que aparecerá, después de 4 pulsos de clock a la salida del último flip-flop.

Del mismo modo, si el shift-registers se carga en paralelo, el bit menos significativo (LSB) debe entrar en el último flip-flop, de modo que en la lectura sea el primero en salir.

En los proyectos que utilicen shift-register, el orden de entrada y salida de los bits es muy importante para obtener el correcto funcionamiento del aparato.

11.4 – Shift-registers o registradores de desplazamiento integrados

Podemos encontrar los registradores del desplazamiento en las familias de la TTL y del CMOS. Los mismos tipos encontrados en la familia TTL normal también se pueden encontrar en las diferentes subfamilias.

Por supuesto, la velocidad máxima de funcionamiento de cada tipo depende de la familia a la que pertenezca.

Vamos a dar algunos ejemplos de circuitos integrados comunes que pueden ser utilizados en proyectos, analizando sus principales características.

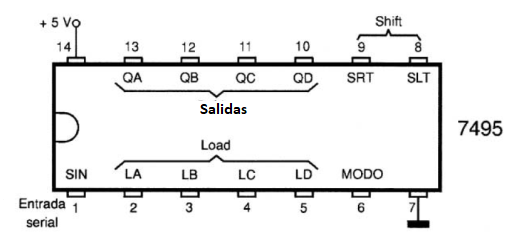

7495 – SHIFT REGISTER DE 4 BIT - (De la izquierda a la derecha - entrada y salida paralela)

Este circuito TTL integrado puede funcionar de dos maneras: Shift o Load. En la figura 92 tenemos su pinaje.

Para operar en el modo de shift, simplemente coloque la entrada MODE en el nivel bajo. Una transición de nivel alto al nivel bajo en la entrada del clock SRT mueve los datos de un paso a la derecha.

Una transición de nivel alto a bajo en la entrada SLT mueve el dato en sentido inverso. Es interesante notar que este circuito utiliza dos clocks, uno para mover los datos a la derecha y el otro a la izquierda.

En el modo Load, esta entrada debe ir al nivel alto, y la información cargada en las entradas LA, LB, LC y LD entran en el circuito en la transición del nivel alto parte inferior de la entrada de comando en la entrada Shift-Left (SLT).

La frecuencia de funcionamiento máxima de un 7495 standard es 36 MHz. las velocidades de funcionamiento más altas se pueden alcanzar con los tipos del LS.

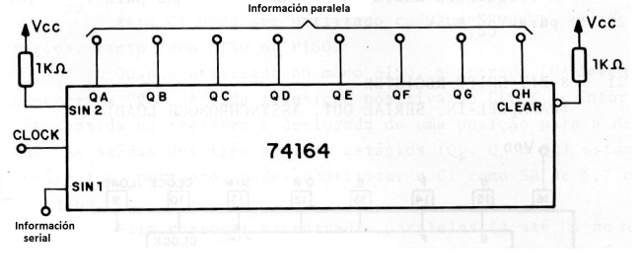

74164 – SHIFT REGISTER DE 8 BITS (Entrada serie, salida paralela)

En la figura 93 tenemos el pinaje de este shift-register TTL.

Este circuito integrado se puede utilizar en la configuración de serial in/serial out o todavía serial in/parallel-out, o sea entrada y salida serie, o entrada de datos en serie y salida en paralelo.

En el funcionamiento normal, una de las salidas serie se mantiene en el nivel alto y los datos se aplican a la segunda entrada serie. La entrada Clear se mantiene en el nivel alto y, en cada pulso desde el punto bajo hasta la parte superior del clock, los datos se mueven de una etapa del circuito.

El contenido del shift-register se puede poner en cero en cualquier momento, tomando la entrada Clear por un instante a un nivel bajo. La frecuencia de funcionamiento máxima de este circuito en la serie standard es de 36 MHz.

Los componentes equivalentes de algunas subfamilias pueden alcanzar frecuencias bien mayores de operación.

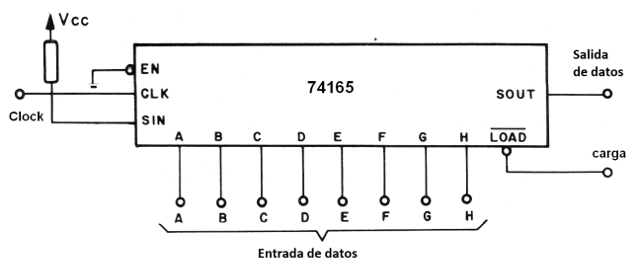

74165 - SHIFT REGISTER DE 8 BITS (Entrada Paralela, salida serie)

Este circuito integrado TTL contiene un shift-register de 8 bits con entrada paralela y salida de datos serie. El pinaje se muestra en la figura 94.

Para el funcionamiento normal, en debe estar en el nivel bajo y LOAD en el nivel alto. En estas condiciones los datos se cambian de puesto de una etapa en la transición positiva de la señal de clock.

Cuando la entrada LOAD se lleva al nivel bajo, el contenido de las entradas de A hasta H se carga en el registrador.

Haciendo EN = 0 y LOAD = 1 los datos se desplazan de un paso en el circuito a cada transición positiva de la señal del clock. El último paso del circuito tiene acceso a la salida complementar.

Para los circuitos integrados de la serie normal la frecuencia de clock máxima es 26 MHz y la consumición por la unidad 42 mA.

Los siguientes son algunos de los registradores de desplazamiento de la familia CMOS.

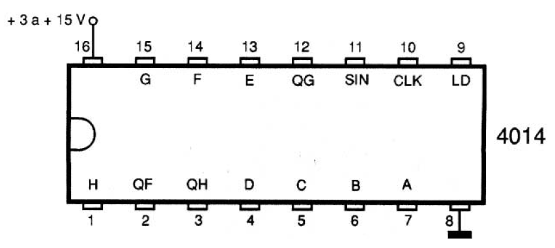

4014 - SHIFT REGISTER ESTÁTICO DE 8 BITS (Entrada paralela y salida serie)

Este circuito integrado CMOS tiene el pinaje mostrado en la figura 95.

Un control de serie/paralelo controla la entrada y permite los pasos individuales de cada una de las 8 etapas. Las salidas Q están disponibles en las etapas 6, 7 y 8. Todas las salidas pueden suministrar o drenar la misma intensidad de corriente.

Cuando la entrada del control paralelo/serie está en el nivel bajo, los datos son cambiados por el circuito a cada transición positiva de la señal del clock.

Cuando la entrada de control está en el nivel alto, los datos se aplican a cada paso del shift-register con la transición positiva del clock.

La frecuencia de funcionamiento máxima de este tipo de circuito depende de la tensión de alimentación. Para una alimentación de 10 volts es la frecuencia está en el orden de 5 MHz cayendo a 2,5 MHz con una alimentación de 5 volts.

En la tabla debajo de las características eléctricas de este IC:

|

Característica |

Condiciones (Vdd) |

Valor |

|

Corriente de desagüe/salida suministrada (TIP) |

5 V 10 V 15 V |

0,88 mA 2,25 mA 8,0 mA |

|

Frecuencia máxima del clock |

5 V 10 V 15 V |

4 MHz 12 MHz 16 MHz |

|

Corriente reposo (máx) |

5 V 10 V 15 V |

0,1 mA 0,2 mA 0,3 mA |

|

Banda de tensiones de la alimentación |

3 V a 15 V |

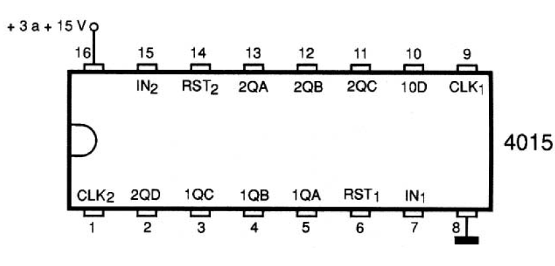

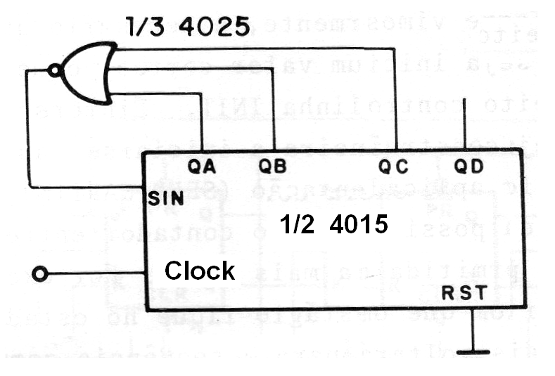

4015 - DOS SHIFT REGISTERSS DE 4 - (Entrada serie, Salida paralela)

El pinaje de este circuito se suministra en la cubierta DIL de 16 pinos' que se muestra en la figura 96.

En este circuito integrado encontramos dos shift-registers que se pueden utilizar de forma independiente.

En la operación normal, RST debe ser colocado en el nivel bajo. Tomando esta entrada al nivel alto el circuito resetea el correspondiente shift-registers tomando todas sus salidas a nivel lógico 0.

Los datos se cambian de puesto a cada transición positiva del pulso del clock.

En la tabla le damos las principales características eléctricas de este CI:

|

Característica |

Condiciones (Vdd) |

Valor |

|

Corriente de desagüe/salida suministrada (TIP) |

5 V 10 V 15 V |

0,88 mA 2,25 mA 8,8 mA |

|

Frecuencia máxima del clock |

5 V 10 V 15 V |

3,5 MHz 8 MHz 11 MHz |

|

Corriente reposo (máx) |

5 V 10 V 15 V |

5 mA 10 mA 150 mA |

|

Banda de tensiones de alimentación |

3 V a 15 V |

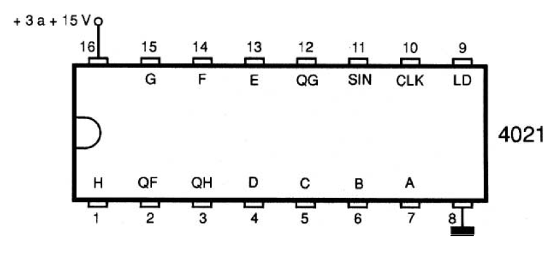

4021 - SHIFT REGISTER DE 8 BITS (Parallel in, Serial out)

Este circuito integrado, cuyo pinaje se muestra en la figura 97, es similar a 4014.

La diferencia radica en el hecho de que la carga (LOAD) puede realizarse de forma asincrónica. Esto significa que es La entrada no depende de la señal del clock.

En la tabla tenemos las principales características eléctricas del 4021.

|

Característica |

Condiciones (Vdd) |

Valor |

|

Corriente de desagüe/salida suministrada (TIP) |

5 V 10 V 15 V |

0,88 mA 2,25 mA 8,8 mA |

|

Frecuencia máxima del clock |

5 V 10 V 15 V |

3,5 MHz 10 MHz 16 MHz |

|

Corriente reposo (máx) |

5 V 10 V 15 V |

0,1 mA 0,2 mA 0,3 mA |

|

Banda de tensiones de la alimentación |

3 V a 15 V |

11.5 – Usando shift-registers

Hay muchas aplicaciones prácticas para los shift-registers. A continuación, repasaremos algunos de ellos:

Conversión Serie/Paralelo y Paralelo/Serie

Una de las aplicaciones más comunes de los registros de desplazamiento es la conversión de información de forma paralela a serie y de serie a paralela.

En la figura 98 damos un ejemplo de cómo podemos convertir una secuencia de bits transmitidas en serie por una línea en un conjunto de salidas paralelas que coincidan exactamente con estos bits.

Este tipo de aplicación se puede encontrar en los módems, y otros sistemas de transmisión de datos en serie, que reciben un flujo de bits en una sola línea y que debe ser transferido a una salida paralela en 8 líneas, que es el modo de operación de los equipos.

Este circuito emplea un shift-registers de tipo SIPO (Entrada en Serie y Salida Paralela).

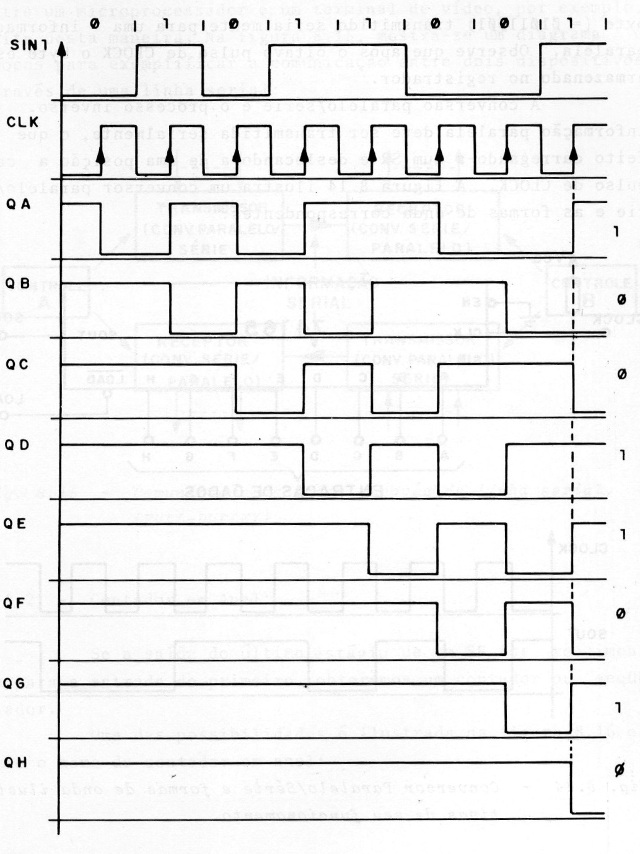

Utilicemos el diagrama de tiempo de la figura 99 para ilustrar cómo funciona y cómo aparece el flujo de datos en serie en su salida.

En la primera línea del gráfico de tiempo tenemos la secuencia de niveles lógicos que se aplica a la entrada del circuito y que corresponde precisamente a la información serial que debemos hacer paralela.

Vea que dos bits 1 seguido no tienen una "separación", pero se distinguen por el tiempo que corresponde a dos ciclos de clock.

En la segunda línea tenemos la señal del clock que sincronizará la transferencia de estas señales a lo largo del registro de desplazamiento.

En las siguientes líneas tenemos la carga de las señales moviéndose por el shift-register hasta que al final del octavo ciclo de clock la señal está presente en todas las salidas del circuito en forma paralela.

La transformación de los datos de forma paralela a la de serie es también muy importante en las aplicaciones digitales que implican información en forma digital. Los datos de las líneas paralelas del ordenador deben ser serializados para ser transmitidos a través de una línea telefónica, por ejemplo.

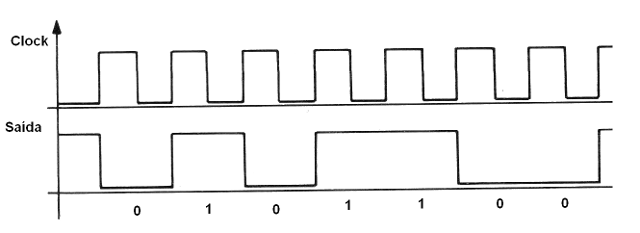

Podemos usar un shift-registers como el 74165 para hacer esto. La figura 100 muestra el modo de conexión de este componente.

Las señales se aplican a las entradas de datos y, con un comando LOAD, se cargan en el shift-registers. Después de eso, en cada pulso del clock las señales se transfieren, bit por bit, a la salida.

La forma de las señales para una secuencia de datos 0101100 se muestra en la figura 101.

Contadores en anillo

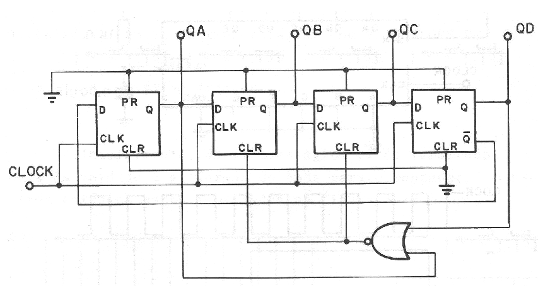

Otra aplicación importante para los registros de desplazamiento es el contador de timbre o el " ring counter". Este tipo de circuito se obtiene cuando se reaplica la salida de shift-register a su entrada, como se muestra en la figura 102.

En este circuito, cargando la primera etapa con el bit 1 y manteniendo las otras con 0. Para ello, se utiliza la línea INIT.

En cada pulso de clock que se aplica al circuito el bit 1 se desplazará de una etapa y cuando llegue a la última, será "realimentado" pasando a la primera. En este circuito, en cada instante, dependiendo de la cantidad de pulsos aplicados, el bit 1 estará presente en una de las salidas del circuito.

La tabla verdad para este tipo de circuito, Con n flip-flops, se muestra a continuación.

|

Pulso de Clock |

Q1 |

Q2 |

Q3 |

... |

Qn-1 |

Qn |

|

0 |

1 |

0 |

0 |

|

0 |

0 |

|

1 |

0 |

1 |

0 |

|

0 |

0 |

|

2 |

0 |

0 |

1 |

|

0 |

0 |

|

... |

|

|

|

|

|

|

|

n-1 |

0 |

0 |

0 |

|

0 |

1 |

|

n |

1 |

0 |

0 |

|

0 |

0 |

Vea que una condición importante para el funcionamiento de este circuito es que comienza a trabajar con el valor correcto colocado en la primera etapa o en la etapa que usted desea.

Se puede asegurar que el circuito comience a funcionar siempre con la "programación" correcta con el uso de un circuito apropiado. Cuando el contador tiene esta característica, decimos que es un circuito " self start ".

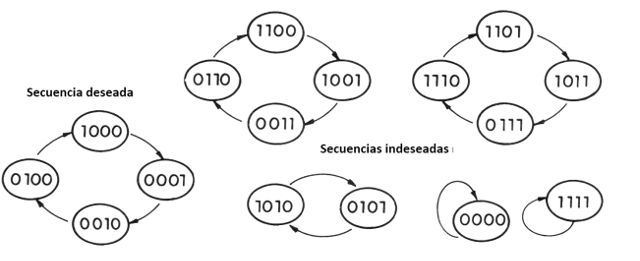

Otro problema que puede ocurrir con un contador de anillos es que adquiere una secuencia de Estados a las salidas de las etapas de las que ya no es capaz de salir, como se muestra en la figura 103.

Esto requiere que el circuito tenga recursos para corregir este problema, que se puede lograr con lo que se llama "auto-corrección" o " self correcting ".

El circuito que se muestra en la figura 104 tiene los recursos indicados para una secuencia de 10 etapas. En otras palabras, se trata de un contador en anillos de 10 etapas con la función de self-correcting y self-start.

En este circuito, QD es el bit más significativo o MSB.

Utilizando otros circuitos integrados, incluyendo la tecnología TTL, podemos implementar más contadores de más etapas.

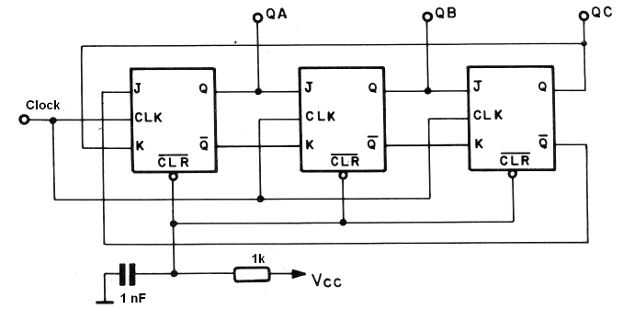

El contador de Johnson

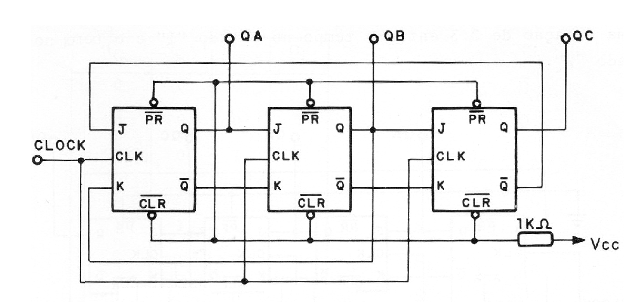

En este tipo de contador la salida complementar de la última etapa es que realimenta la entrada del circuito. En la figura 105 tenemos un ejemplo de contador Johnson de 4 etapas utilizando flip-flop tipo J-K.

Cuando la alimentación del circuito se establece todos los flip-flop son reseteados. Esto se consigue mediante la red formada por el resistor de 1 K ohms y el capacitor de 1 nF.

Lo que ocurre es que en el momento en que se establece el tensión en el circuito se descarga el capacitor. En este momento, con la corriente fuerte de la carga que fluye a través del capacitor la tensión en su armadura es virtualmente cero que es este nivel establecido en las entradas de CLR de los flip-flops lo que los resetea.

Una fracción de segundo más adelante, con la carga del capacitor que es alcanzada, la corriente en el circuito deja de fluir y el nivel lógico en las entradas de CLR va alto, soltando su operación.

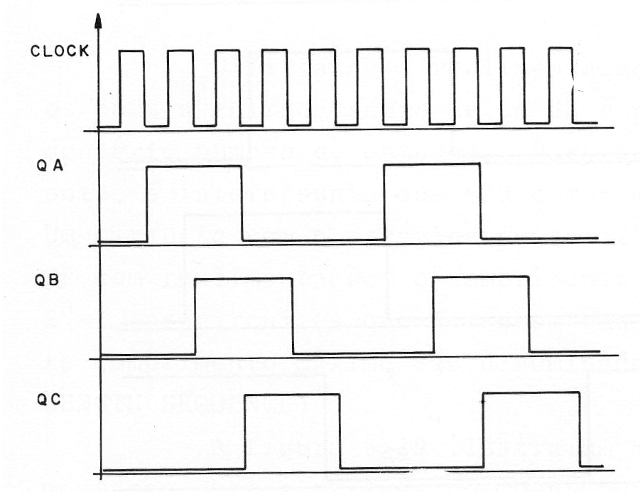

En la figura 106 tenemos las formas de onda en las salidas de este circuito.

Vea que la frecuencia de la señal del clock está dividida por 8 en este circuito. De hecho, la frecuencia será dividida por un número que será el doble del número de etapas del circuito. Por ejemplo, un contador de 5 etapas divide la frecuencia de entrada por 10.

Un problema que puede ocurrir con este tipo de circuito es la entrada en un estado que no está permitido y de la que no puede irse. Si esto ocurre, el circuito queda atrapado en una secuencia incorrecta de valores digitales que se muestran en la salida.

Una manera de evitar esto se muestra en la figura 107 donde tenemos un contador de 4 etapas utilizando los flip-flops disponibles en los circuitos integrados CMOS del tipo 4013 y, además, de eso un puerta NOR 4001.

En este circuito, las entradas de CLR de los flip-flops intermedios se utilizan para remontar el circuito cuando un estado prohibido que es, por ejemplo, los niveles 1 en las salidas, al mismo tiempo, de la primera y última etapa ocurran.

En la figura 108 tenemos otro circuito de contador Johnson con el módulo 3.

Las formas de onda se dan en la figura 109.

Este circuito se caracteriza por el hecho de que permite contar en módulos de valores impares. Nótese que los circuitos siempre pueden ser modificados para lograrlo, lo cual puede ser importante en proyectos prácticos.

Sumário

Curso de Electrónica - Electrónica Digital (CUR5000)

Curso de Electrónica - Electrónica Digital – Parte 1 (CUR5001S)

Curso de Electrónica Digital – Parte 2 - El Álgebra de Boole (CUR5002S)

Curso de Electrónica - Electrónica Digital - Parte 6 - Los Elementos Biestables (CUR5006S)

Curso de Electrónica - Electrónica Digital - Parte 9 - Contadores Digitales (CUR6002S)

Curso de Electrónica - Electrónica Digital - Parte 13 - Memorias, ADCs y DACs (CUR6006S)