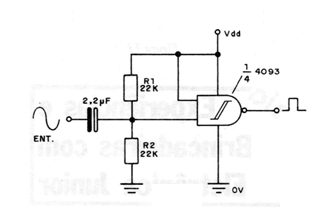

El circuito presentado en la figura convierte una señal senoidal de amplitud conveniente en una señal rectangular compatible CMOS. Los resistores R1 y R2, típicamente de 22 k, determinan la impedancia de entrada del circuito que C1 debe tener su valor elegido en función de la frecuencia de la señal senoidal de excitación. El condensador debe presentar una baja reactancia en la frecuencia elegida. Una aplicación práctica de este circuito es como reloj para los relojes sincronizados a partir de la red de alimentación. Una señal sinusoidal de 60 Hz puede convertirse en una señal rectangular de 6oHz para una posterior selección en etapas CMOS.